# **Components & System Solutions**

Smart sensor emulation for FPGA based systems

electronics4U

## **TRS-STAR Tec Bytes**

electronics4U

With the TEC BYTES webinars, TRS-STAR offers you bite-sized technical tidbits.

TRS-STAR customers are cordially invited to this free training opportunity.

https://www.trs-star.com/en/mediathek/webinars

## **On-Demand Webinars**

electronics4U

# On-Demand Webinars require registration Tec Bytes on YouTube does not require registration

#### On-Demand Webinars

#### Introduction to FPGA design with Efinix

Presenter: FH-Prof. DI Dr. Markus Pfaff (CEO & Co-Founder P2L2),

Andreas Schwarztrauber (CEO TRS-STAR)

Language: English

PDF Flyer

Register

## Tec Bytes on Youtube

#### Design Flow (Tutorial)

Presenter: Harald Werner Duration: 0:21:56 h Language: English

## **Upcoming Webinars in September (1)**

TCS-STAC

electronics4U

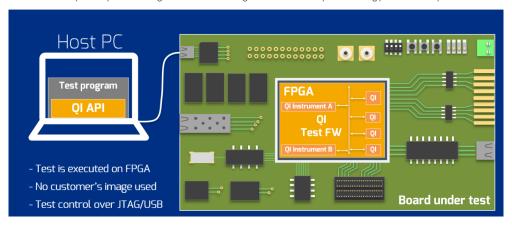

# **Introduction to Quick Instruments**

#### Quick Instruments

#### Test framework for FPGA board quality control

**Quick Instruments (QI)** is a test & measurement framework that loads itself into on-board FPGA for test, validation or programming purposes. The role of instruments is to verify PCBA hardware infrastructure: on-board interconnections and communication with peripheral components. In this way, every PCBA board can be checked for defects and stability issues. All instruments are pre-compiled for a target board and are being executed from test platform using predefined templates.

## **Upcoming Webinars in September (2)**

electronics4U

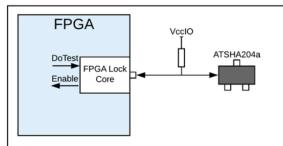

## Prevent Overbuilding and secure your design with the FPGA Lock IP

The FPGA Lock is a small FPGA IP core that prevents overbuilding and cloning of your FPGA-based systems and consequently protects your revenue. It can also be used to guarantee hardware integrity in Safety Critical, Medical or Military/Defence applications.

- Test triggered, core Reads device ID.

- Core sends 256 bit random challenge.

- 3. ATSHA204a perfoms SHA256 hash on the challenge, its ID and a programmed 256 bit secret key. The hash result is returned to the core.

- 4. The core also performs the hash on the challenge, device ID and secret key (that it knows).

- challenge, device to and secret key (that it knows).

If the two sets of hash results match then a device with the correctly programmed secret key is present, FPGA functionality is enabled.

## **Upcoming Webinars in September (3)**

electronics4U

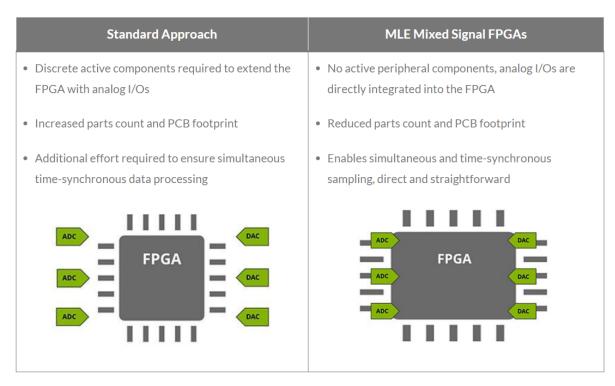

# Implementing ADCs and DACs in digital FPGAs

## **Smarte Sensor Emulation für FPGA basierte Systeme**

electronics4U

**SmartWave**

Communication (I2C, SPI, UART, GPIOs)

**Emulation**

(corner cases)

**Demos**

**FPGA + Sensors**

electronics4U

#### **Timeline:**

- NOW T\*Square T20-100 Education Board\*

- NOW T\*Square T20-144 Education Board

- 11/24 T\*Square Ti60-256 Education Board

\*) with 16 Mbit integrated SPI-Flash

- Rapid Prototyping

- Measure power consumption on all voltage rails

- RISC-V (Sapphire) evaluation

- UART to RISC-V

- Evaluation of ADCs/DACs in an digital FPGA

- Break-Out-On-Board-Programmer

#### Be creative with T\*Square Boards

electronics4U

## https://www.trs-star-shop.com/index.php/en/fpga-en/evalboards-en/product/t-square-t20-144-education-board

# TCS-STAC

## **FPGA**

Procuct brief

Product Documentation

Reference Design

Possible Breakout FTDI for UART 1/2 USB JTAG Programming **UART Communication** 3.3V suppl GPIO Connector Bank 1 GPIO / PMOD SPI 16Mbit **EFINIX** Flash **FPGA** Trion/Titanium CLK OSC 10 MHz **GPIO** 2.5V or 3.3V supplied 00 1.2V 2.5V 3.3V USB 2.D Opt. PWR IN DC/DC Switch LDO → 5V to 1.2V 5V to 3.3V PG EN DC/DC Connector Bank 3 -3CH 5V to 2.5V **Power Supply** ADC 2.5V 3CH DAC Connector Bank 4 - 2.5V or 3.3V supplied Differential I/Os

electronics4U

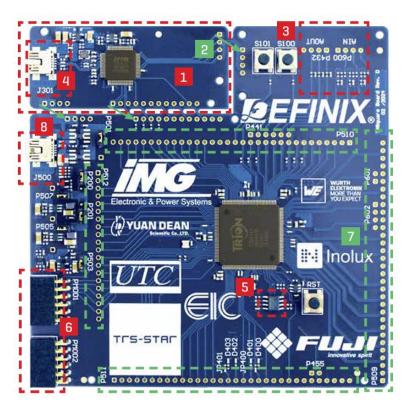

- 1 Break-Out-Board with Programmer Break-Out to use it for your own boards

- There is still the option to continue to use the programmer in combination with the T\*Square Education Board

- 3 External R-C-circuitry allows implementation of ADCs and DACs in a digital FPGA, using LVDS-Buffers for sigma-delta-ADCs

- 4 A UART allows communication with the RISC-V Saphire Soft-Core that can be implemented in the FPGA Core fabric

- The PCB allows to mount either 100-pin LQFP (with integrated SPI-Flash) or 144-pin LQFP (with external SPI-Flash)

- 6 2 x PMOD interfaces allow attaching PMOD daughter cards

- Post connectors (included, but not mounted) can be mounted on the top or bottom of the T\*Square education board to connect your own basedboards or daugther cards

- 8 Alternative USB-Connector for Board Power Supply, when Break-Out-Programmer (1) is removed

## **Disruptive FPGA technology**

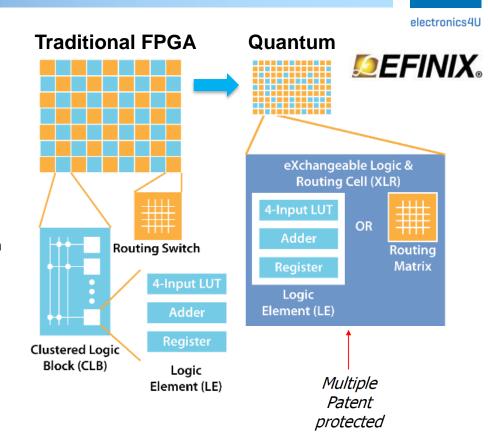

### **Quantum FPGA Technology from Efinix**

**XLR** eXchangeable Logic or Routing Cell (the decision is made at compile time)

#### **Resulting in Advantages over traditional FPGAs**

- Optimal resource usage -> smaller dies

- ✓ Cost benefit

- ✓ Small packages -> less PCB real estate -> compact systems

- Less transistors, shorter routing -> less Power Consumption

-> less cost

- 7 layers of metal vs.12+ layers -> reduced NRE cost

- Cost benefit, more flexibility to adjust to customer needs

- Single architecture scalable to 1 Mio+ LEs

- Standard process and Silicon process agnostic

- ✓ Could be transferred to other fabs

- ✓ Short Leadtimes, even during allocation!

## **Disruptive FPGA technology**

electronics4U

https://www.trs-star.com/en/mediathek/webinars

#### Introduction to FPGA design with Efinix

Presenter: FH-Prof. DI Dr. Markus Pfaff (CEO & Co-Founder P2L2),

Andreas Schwarztrauber (CEO TRS-STAR)

Language: English

### electronics4U

www.trs-star.com

#### **TRS-STAR GmbH**

Headquarters | Sales · Marketing

Sales Europe

Werner-von-Siemens-Str. 1

76297 Stutensee

T +49 7249 95222-0

info@trs-star.com

Logistics · Sales · Engineering

Schraderstraße 44 67227 Frankenthal T +49 6233 347-0

info@trs-star.com

Switzerland

Hofstrasse 87

8620 Wetzikon (Zürich)

T +41 76 3778343

ceko@trs-star.com

France

14 allée de la Vaudonnière

91370 Verrières le Buisson

T +33 614 932518

commelin@trs-star.com

UK

15, Oakley Close, Addlestone,

Surrey. KT15 2LT

T +44 1932 483040

bonnett@trs-star.com

Romania

bd Ion Mihalache 319, bl 21, ap 15

011184 Bucharest 1

T +40 72 3569406

balanescu@trs-star.com